1. Jurnal[Back]

2. Alat dan Bahan[Back]

A. Alat dan bahan pada percobaan praktikum

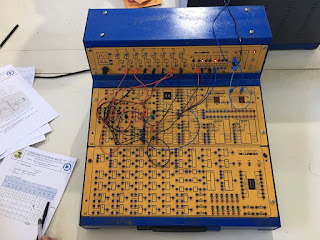

> Module D'Lorenzo

- Sebagai tempat merangkai rangkaian

> Panel DL 2203C

> Panel DL 2203D

> Panel DL 2203S

> Jumper

- Sebagai media penyalur arus listrik

> IC 74LS112

- digunakan pada rangkaian yaitu J-K flip flop

> IC 7474

- digunakan pada rangkaian yaitu D flip flop

> Logic probe

-digunakan untuk melihat logika pada output

> switch

- switch SW-SPDT merupakan golongan saklar yang memiliki 3 terminal, jenis switch ini digunakan sebagai saklar pemilih. Contohnya saklar pemilih tegangan input adaptor yaitu 110v, dan 220v.

> VCC

-digunakan sebagai sumber arus

3. Rangkaian Simulasi[Back]

4. Prinsip Kerja Rangkaian[Back]

Di rangkaian B1 itu berlogika 1 merupakan input dari S sehingga S berlogika 1, dan B2 yang berlogika 0 terhubung ke kaki J sehingga J berlogika 0. Kemudian B4 yang berlogika 1 dihubungkan dengan K sehingga K juga berlogika 1.

Prinsip dari R dan S yaitu aktif low, dimana ia akan aktif ketika input R dan S berlogika 0. Dan pada rangkaian tampak input dari S dan R sama - sama 1, maka yang akan memengaruhi aoutput yaitu kaki J dan K.

Kemudian D flip-flop, disini switch SPDT untuk kaki highnya terhubung ke vcc dan bagian low nya ke ground. untuk B5 dan B6 mendapatkan arus langsung dari VCC sehingga berlogika 1. B5 terhubung dengan D sehingga D berlogika 1 dan B6 terhubung ke clock sehingga clock berlogika 1. Dan untuk R dan S mendapat input dari B1 dan B0 yang berlogika 1.

Dalam kondisi ini R dan S tidak aktif dikarenakan inputnya yang berlogika 1, sehingga yang aktif untuk memengaruhi output yaitu D.

Dan ketika percobaan menggunakan Module D'Lorenzo kita merangkainya sesuai dengan modul dimana kaki S dihubungkan ke B1, kaki 1J ke B2, C1 ke B3, 1K ke B4, R ke B0 (untuk J-K flip-flop) dan S ke B1, 1D ke B5, C1 ke B6, R KE B0 (untuk D flip - flop). Data kita dapat dengan cara mengubah2 kondisi sesuai dengan jurnal dan untuk yang ada clocknya maka caranya diubah dulu seluruh kaki sesuai kondisi dan baru clocknya yang di pindahkan. Jika tidak begitu maka data yang di dapat akan salah.

Ketika dicobakan, input logikanya diatur dimana B0 = 0 dan B1 = 1 kemudian untuk kaki input lainnya don't care (ketika don't care itu berlogika 0). Maka akan dihasilkan output pada J-K flip flop di kaki Q = 0 dan Q' = 1. Pada D flip flop output pada kaki Q = 0 dan Q' = 1.

Ketika logika input B1 = 0 dan B0= 1 dan untuk kaki lainnya yaitu don't care (ketika don't care itu berlogika 0). Maka akan didapatkan output untuk J-K flip flop pada Q=1 dan Q' = 0 kemudian D flip flop Q=1 dan Q'=0

Kemudian logika input diubah lagi B0 = 0 dan B1 = 0 dan untuk kaki lainnya yaitu don't care (ketika don't care itu berlogika 0). Maka akan di dapat output untuk J-K flip flop pada Q = 1 dan Q'=1 kemudian D flip flop Q= 1 dan Q'=1. Dengan kondisi tersebut dimana seluruh outputnya bernilai 1 menghasilkan kondisi yaitu kondisi terlarang.

5. Video Rangkaian[Back]

6. Analisa[Back]

> Bagaimana jika B0 dan B1 sama - sama diberi logika 0, apa yang terjadi pada rangkaian?

Jawab : Sesuai dengan percobaan yang telah dilakukan dan data yang didapat, ketika B0 dan B1 sama - sama berlogika 0 maka input R dan S juga 0. Setelah dilakukan percobaan, terjadi kondisi terlarang pada kedua flip-flop dimana Q dan Q'nya bernilai 1.

Jawab : Ketika B3 diputus, maka yang terjadi ketika B0 dan B1 berlogika 0 yaitu tetap terjadi kondisi terlarang, yaitu outputnya 1. Namun ketika B1 = 1 dan B0 = 0 maka yang terjadi yaitu logika B0 = Q dan B1 = Q' dan bisa kita katakan sesuai kondisi ini, clocknya tidak aktif.

> Jelaskan apa yang dimaksud dengan kondisi toggle, not change, dan kondisi terlarang pada flip - flop !

Jawab :

A. toggle : Kondisi yang terjadi pada rangkaian flip - flop ketika output yang terjadi merupakan kebalikan dari output sebelumnya. Sesuai dengan tabel rangkaian percobaan 1 pada J-K flip - flop dimana output data ke7 itu 0 dan 1 sedangkan sebelumnya 1 dan 0.

B. Not change : Kondisi yang terjadi ketika output yang terjadi sama dengan output sebelumnya.

Jawab :

A. toggle : Kondisi yang terjadi pada rangkaian flip - flop ketika output yang terjadi merupakan kebalikan dari output sebelumnya. Sesuai dengan tabel rangkaian percobaan 1 pada J-K flip - flop dimana output data ke7 itu 0 dan 1 sedangkan sebelumnya 1 dan 0.

B. Not change : Kondisi yang terjadi ketika output yang terjadi sama dengan output sebelumnya.

Tidak ada komentar:

Posting Komentar