1. Jurnal[Back]

2. Alat dan Bahan[Back]

> Panel DL 2203D

> Panel DL 2203C

> Panel DL 2203S

> Jumper

3. Rangkaian Simulasi[Back]

4. Prinsip Kerja Rangkaian[Back]

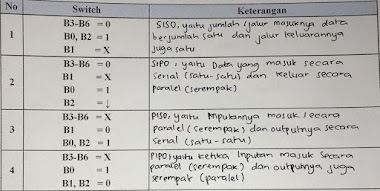

Pada percobaan ini, kita merangkai sebuah rangkaian shift register (register geser) dimana keluarannya berupa 4 bit. Pada rangkaian ini kita menggunakan 4 buah J-K flip flop. Dimana 1 J-K flip flop mewakili 1 bit. Dimana sesuai kondisi pada jurnal maka akan di dapatkan proses operasi yaitu, Pada kondisi 1, sesuai dengan jurnal kita dapat memerhatikan bahwa kondisi 1 merupakan shift register SISO , yaitu jalur masuknya data berjumlah satu dan jalur keluarannya juga satu. Pada kondisi 2, sesuai kondisi jurnal, di dapatkan bahwa kondisi ini berjenis SIPO yaitu data yang masuk secara serial dan keluar secara paralel (serempak).

Pada kondisi 3, didapat bahwa kondisi ini merupakan shift register PISO yaitu ketika inputannya masuk secara paralel ( serempak) dan outputnya secara serial (satu - satu). Pada kondisi 4, di dapat bahwa kondisi ini merupakan shift register PIPO, yaitu ketika inputan masuk secara paralel (serempak) dan outputnya juga secara serempak (paralel).

Terjadinya proses input dan output pada rangkaian ini berarti bahwa proses shift register ini dapat menyimpan memori sementara dari masukan menuju keluaran bit ke 4 dari daerah lingkup 4 bit.

5. Video Rangkaian[Back]

6. Analisa[Back]

> Analisa output yang dihasilkan tiap - tiap kondisi

Jawab :

Pada kondisi 1, sesuai dengan jurnal kita dapat memerhatikan bahwa kondisi 1 merupakan shift register SISO , yaitu jalur masuknya data berjumlah satu dan jalur keluarannya juga satu.

Pada kondisi 2, sesuai kondisi jurnal, di dapatkan bahwa kondisi ini berjenis SIPO yaitu data yang masuk secara serial dan keluar secara paralel (serempak).

Pada kondisi 3, didapat bahwa kondisi ini merupakan shift register PISO yaitu ketika inputannya masuk secara paralel ( serempak) dan outputnya secara serial (satu - satu).

Pada kondisi 4, di dapat bahwa kondisi ini merupakan shift register PIPO, yaitu ketika inputan masuk secara paralel (serempak) dan outputnya juga secara serempak (paralel)

Pada kondisi 2, sesuai kondisi jurnal, di dapatkan bahwa kondisi ini berjenis SIPO yaitu data yang masuk secara serial dan keluar secara paralel (serempak).

Pada kondisi 3, didapat bahwa kondisi ini merupakan shift register PISO yaitu ketika inputannya masuk secara paralel ( serempak) dan outputnya secara serial (satu - satu).

Pada kondisi 4, di dapat bahwa kondisi ini merupakan shift register PIPO, yaitu ketika inputan masuk secara paralel (serempak) dan outputnya juga secara serempak (paralel)

> Jika gerbang AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip flop, bandingkan output yang di dapat.

Jawab :

Ketika terdapat gerbang AND maka kuta dapat menghentikan hitungan pada logic probe di output yang diinginkan. Namun jika tidak ada gerbang AND maka ketika logic probe aktif dan keluarannya counter dan tidak bisa dihentikan pada output yang diinginkan.

Ketika gerbang AND terhubung ke B2 dan berlogika 0, maka clock tidak aktif dan output keluar secara paralel (SIPO dan PIPO). Ketika tidak ada gerbang AND, output tidak dapat keluar secara serentak, jenis shift register yaitu tidak SIPO dan PIPO.

https://drive.google.com/uc?export=download&id=

7. Link Download[Back]

Download HTML [disini]

Download Video Rangkaian [disini]

Download Rangkaian [disini]

Download Datasheet IC 74111 [disini]

Download Datasheet gerbang AND [disini]

Tidak ada komentar:

Posting Komentar